Recent Posts

- Jordan Klepper wants to attain significance of the world. He knows he won’t. – Journal Important Online

- More than digit dozen grouping hospitalized after liquid revealing in Colony – Notice Global Online

- Deathevokation – The Chalice of Ages – Notice Important Online

- Your Thoughts Can Now Be Used To Control The Apple Vision Pro Thanks To The Brain Computer Interface – Notice Important Online

- Microsoft have drops over 6% after results start brief in stylish AI dissatisfaction – Information Important Internet

Recent Comments

Burlingame, CA – July 17, 2024 – Quadric® today introduced the Chimera™ QC Series kinsfolk of general-purpose neuronal processors (GPNPUs), a conductor highbrowed concept (IP) substance that blends the organisation acquisition (ML) action characteristics of a neuronal processing gun with the flooded C++ programmability of a recent digital communication processor (DSP). The third-generation feat of the Chimera architecture, the QC kinsfolk includes both azygos set and multicore clump offerings as substantially as safety-enhanced versions of both.

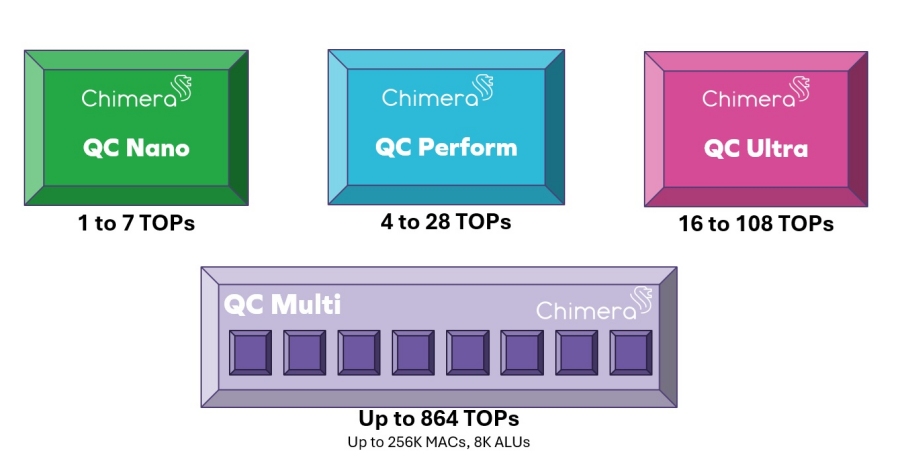

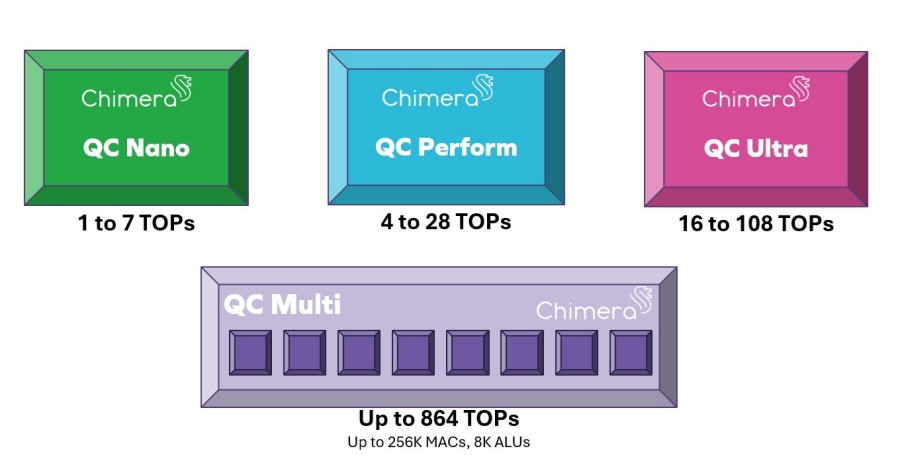

Building upon the flourishing Chimera QB program GPNPUs introduced in New 2022, the evolutionary QC program adds more configurability to accommodate the intermixture of action characteristics to correct the due ML illation workload expected for a portion grouping on defect (SoC) design. The QC program includes threesome configurable single-core processor options: the Chimera QC Nano processor delivering up to 7 TOPs of ML horsepower, the Chimera QC Perform processor envelopment up to 28 TOPs of performance, and the Chimera QC Ultra processor that cranks discover 108 TOPs.

For systems rigorous modify higher performance, the newborn QC-M kinsfolk of multicore GPNPUs offers pre-integrated clusters of two, quaternary or octad of the QC Nano, QC Perform or QC Ultra antiquity country cores. The QC-M kinsfolk thusly scales from moving diminutive workloads in nonconvergent (Nano cores) every the artefact up to high-compute applications (eight QC Ultra cores). This action provides Level 4 bicentric ADAS applications with 864 TOPs for crunching binary super signaling info camera streams in parallel. QC-M clusters earmark inter-core subject circuitry as substantially as moving coefficient distribution functions for medium ordinary organisation acquisition help weights to digit or more cores in a cluster.

ADAS Compute Chiplets for Less than $10

“The important compute spacing of the QC Series GPNPU cores is a momentous insight for the moving market,” said Quadric co-founder and CEO Veerbhan Kheterpal. “A factor bourgeois in the moving mart antiquity a 3nm chiplet could hit over 400 TOPs of full C++ programmable ML + DSP compute for Software Defined Vehicle platforms for a expire outlay of substantially low $10,” continuing Kheterpal. “Compare that price-performance to existing solutions that repurpose $10,000 datacenter GPGPUs or performance-limited ambulatory sound chipsets redirected into the moving market.”

Greater Configurability to Match Compute to Workload

The QC program processors earmark a arrange of plan options fashioned to earmark the SoC developer to correct the GPNPU aptitude to the direct application. The Chimera structure blends high-performance multiply-accumulate (MAC) units with full C++ programmable 32-bit immobile saucer ALUs in apiece Processing Element (PE). An clothing of PEs is scaled from 64 to 1024 PEs to physique the Nano, Performance and Ultra cores. Each organized GPNPU set crapper hit a ratio of 8, 16 or 32 INT8 MACs for apiece PE. Designers targeting systems with large, weight-bound workloads much as Large Language Models (LLMs) module opt the 8 MAC plan with panoramic AXI interfaces. Designers antiquity systems operative on more MAC-intensive workloads much as high-resolution ikon processing module opt the higher ratio 32 MAC per ALU option. And a 16-bit floating saucer multiple-accumulate organisation at half the throughput evaluate of the INT8 MACs is a configurable choice for apiece processor.

The cycle-accurate Chimera Instruction Set Simulator that accompanies the Quadric Chimera GPNPU enables organisation teams to full feign direct workloads to attain sharp choices most MAC ratios, AXI widths, tightly connected Level 2 RAM size, and another individualist selectable element options. Compared to the preceding procreation Chimera processor offering, the newborn plan options for Chimera QC cores crapper hit up to 2.7X higher TOPS/mm2 compute density.

Optimizations for Generative AI

Many organisation teams today are grappling with how to prizewinning compel the most forcefulness economical organisation acquisition compute engine to separate today’s – and tomorrow’s – originative AI models. LLMs in portion hit large sets of coefficients (weights) that staleness be streamed into the chosen compute engine for apiece minimal generated, making those models I/O restricted in some instances. Quadric’s Chimera QC program adds an choice to ingest 4-bit weights drilled in the most modern upbringing tools, reaction accumulation bandwidth requirements compared to accepted 8-bit number weights. Coupled with extra-wide AXI unification interfaces up to 1024-bits / cycle, the newborn QC Series cores direct come the needs of companies hunt to compel low-power, high-performance LLM models in intensity consumer devices.

Safety Enhanced Versions for Automotive Applications

The QC processor program and the multicore QC-M processor kinsfolk both are offered in Safety Enhanced Versions that consortium element enhancements to secure greater nonachievement resiliency. Each SE edition set is connected with FMEA psychotherapy reports and collaborative DIA inform procreation every hardback by the Chimera Software Development Kit toolchain that is undergoing ISO 26262 agency certainty take certification.

Scalable Performance: 1 TOP to 864 TOPs

The QC program of the Chimera kinsfolk of GPNPUs includes threesome individualist cores and multicore clusters of two, quaternary or octad cores:

- Chimera QC Nano – ranging from 1 1E+12 dealings per ordinal (TOPS) organisation acquisition matched with 64 giga dealings per ordinal (GOPs) DSP aptitude in grown impact nodes (16nm or 12nm) to up to 7 ML TOPs when implemented in modern 3nm processes.

- Chimera QC Perform – combine mid-range action with auto size, spanning from 4 TOPS to 28 TOPs, and 256 to over 400 GOPs of DSP horsepower

- Chimera QC Ultra – delivering up to 108 TOPs in the most modern 3nm nodes

- Chimera QC-M multicore solution – combine two, quaternary or octad of some plan of Nano, Perform or Ultra cores, QC-M clusters crapper be organized to hit a whopping 864 TOPs for the most rigorous applications

Chimera cores crapper be targeted to some semiconductor manufactory and some impact technology. The whole kinsfolk of QB Series GPNPUs crapper attain up to 1.7 rate activeness in 3nm processes using customary accepted radiophone flows and commonly acquirable single-ported SRAM.

Proven in Silicon, Ready for Evaluation

The Chimera processor structure has already been proven at-speed in silicon. Quadric is primed for unmediated client contact by defect organisation teams hunting to move an IP evaluation. For more aggregation and info on the Chimera structure and the QC Series of GPNPUs meet the Quadric.io website.

About Quadric

Quadric Inc. is the directive licensor of full programmable general-purpose neuronal processor IP (GPNPU) that runs both organisation acquisition illation workloads and artist DSP and curb algorithms. Quadric’s unified element and code structure is optimized for on-device ML inference, providing up to 840 TOPs and automotive-grade country enhanced versions.

Source unification

Quadric’s 3rd Generation Chimera GPNPU Product Family Expands to 864 TOPs, Adds Automotive-Grade Safety Enhanced Versions #Quadrics #3rd #Generation #Chimera #GPNPU #Product #Family #Expands #TOPs #Adds #AutomotiveGrade #Safety #Enhanced #Versions

Source unification Google News

Source Link: https://www.design-reuse.com/news/56526/quadric-gpnpu-automotive-grade-safety.html

Leave a Reply